| 【深度教学3】Altera EP4CE6F17C8 FPGA驱动数码管动态显示全攻略 | 您所在的位置:网站首页 › fpga 开发板 驱动 win xp win 7 › 【深度教学3】Altera EP4CE6F17C8 FPGA驱动数码管动态显示全攻略 |

【深度教学3】Altera EP4CE6F17C8 FPGA驱动数码管动态显示全攻略

|

一、电路模块

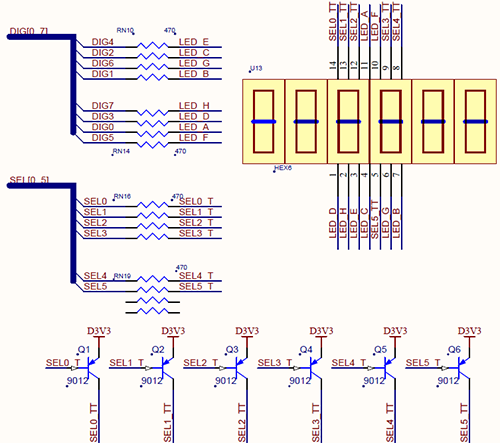

1、数码管 开发板板载了6个数码管,全部为共阳型,原理图如下图所示,段码端引脚为DIG[0]~DIG[7]共8位(包含小数点),位选端引脚为SEL[0]~SEL[5]共6位。端口均为低电平有效。

其实物图如下所示。

数码管引脚分配见下表。

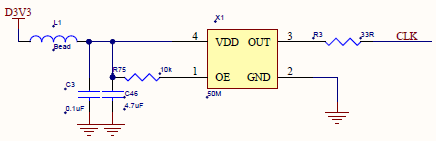

2、时钟晶振 开发板板载了一个50MHz的有源晶振,为系统提供时钟。

其实物图如下所示。

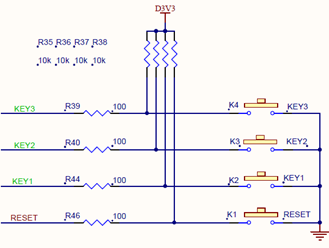

时钟输出引脚分配见下表。

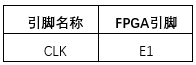

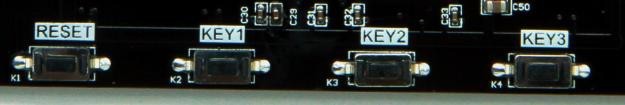

3、按键 开发板板载了4个独立按键,其中有3个用户按键(KEY1~KEY3),1个功能按键(RESET)。按键按下为低电平(0),释放为高电平(1),4个按键的原理图如下图所示。本例中只使用了RESET键。

其实物图如下所示。

按键的引脚分配见下表。

本例实现6个数码管显示123456,代码使用Verilog编写,采用例化的形式,共有两个文件。 先编写数码管实现字形的程序,模块名称为seg,文件名称为seg.v,代码如下。 module seg( input[3:0] data, //显示的字形,可显示0~F十六个字形,所以需要4位 output reg[7:0] seg //字形编码,包含小数点,共8位 ); always@(*) //敏感信号为所有输入量 begin case(data) 4'd0:seg |

【本文地址】

公司简介

联系我们